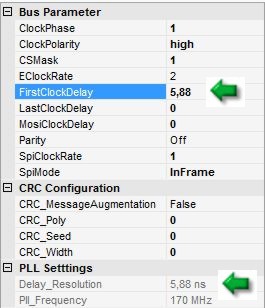

The delay time between activated CS and the first clock of data transmission can be defined with the parameter FirstClockDelay.

The input value has to be entered as a multiple factor of the Delay-Resolution.

The Delay-Resolution is a time value, which results from the internal crystal rate and the entry of the SPI clock rate. Therefore the Delay-Resolution can not be defined but applies the step size of delay time values.

Example of a FirstClockDelay-

entry:

Delay-Resolution at a SPI-Clock of 1 MHz = 5,88 ns

Results to an input value for the FirsClockDelay:

1x5,88 ns=5,88 ns or

2x5,88 ns=11,76 ns or

3x5,88 ns =17,64 ns and so on.

The entry of values between the step size causes that the next smaller multiple value of the Delay Resolution will be entered.

The entry will be done at the SPI-Bus-Configuration window by direct value input in [ns].

| Procedure | |

|

Open the SPI-Bus-Configuration window. |

|

Enter the both parameters in the desired field of the section Bus-Parameter by clicking on the field. |