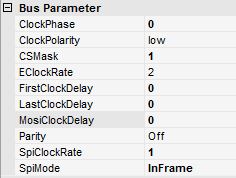

| Parameter | Description | Value | Predefined: |

||||||||||||||||||||||||||||||||||||||||||||||||

| ClockPhase | Defines

the slope of the clock impulse when the data transfer occurs.

Detailed description |

0

= Data transfer with rising edge.

1 = Data transfer with falling edge. |

0 | ||||||||||||||||||||||||||||||||||||||||||||||||

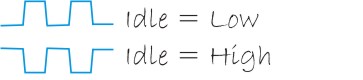

| ClockPolarity | Defines

the polarity of the clock signal.

Detailed description |

Low

= Idle is low-signal

High = Idle is high signal |

low | ||||||||||||||||||||||||||||||||||||||||||||||||

| CSMask | Number

of the used CS-lines as bit decoded mask. CS 0 = 0001 CS 1 = 0010 CS 2 = 0100 CS 3 = 1000 and all combinations of it, for example: Use of CS1 and CS3 = 0101 or Use of all 4 possible CS lines =1111 Detailed description |

Input

of the decimal value of the dual number:

|

1 | ||||||||||||||||||||||||||||||||||||||||||||||||

| EClockRate | Optional

clock impulse frequence for sensors if they need one.

The EClockRate signal is being offered at the 25-pol. SUB-D-connector pin 23. |

Direct

value entry in [MHz] from 0,01 to 5 MHz. |

2 | ||||||||||||||||||||||||||||||||||||||||||||||||

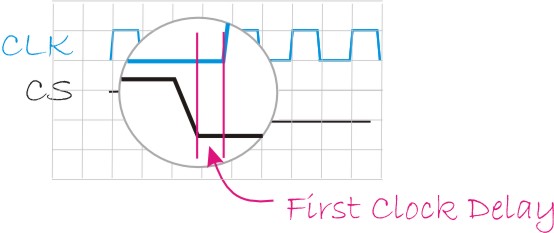

| FirstClockDelay | Delay

time between activated CS and Clock impulse.

Detailed description |

Direct

value entry in [ns]. Only input values, which are multiples of the delay resolution values are valid. |

0 | ||||||||||||||||||||||||||||||||||||||||||||||||

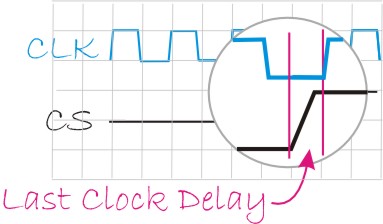

| LastClockDelay | Delay

time between last clock an deactivated CS.

Detailed description |

Direct

value entry in [ns]. Only input values, which are multiples of the delay resolution values are valid. |

0 | ||||||||||||||||||||||||||||||||||||||||||||||||

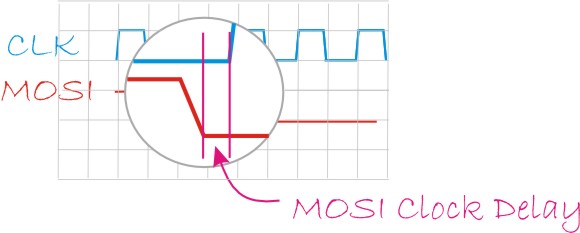

| MosiClockDelay | Delay

time between clock impulse and MOSI data changel.

Detailed description |

Direct

value entry in [ns]. Only input values, which are multiples of the delay resolution values are valid. |

0 | ||||||||||||||||||||||||||||||||||||||||||||||||

| Parity | Definition

of the kind of error detection. Following variations are available:

|

OFF=No

error detection

EVEN= Even parity-error detection ODD=Odd parity-detection CRC=CRC error detection (The configuration of the CRC-error detection is done at the parameter section CRC-Configuration) |

Off | ||||||||||||||||||||||||||||||||||||||||||||||||

| SpiClockRate | Frequence

of the clock impulse in MHz

Detailed description |

Direct value input in [MHz] from 0,01 to 20 MHz. | 2 | ||||||||||||||||||||||||||||||||||||||||||||||||

| SpiMode | Selection

of the SPI protocol

Detailed description |

Inframe or outframe | Inframe |